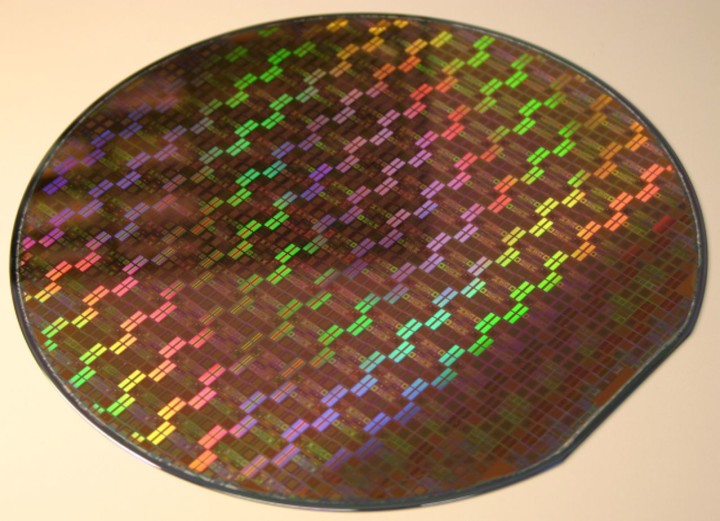

Patterned Wafer

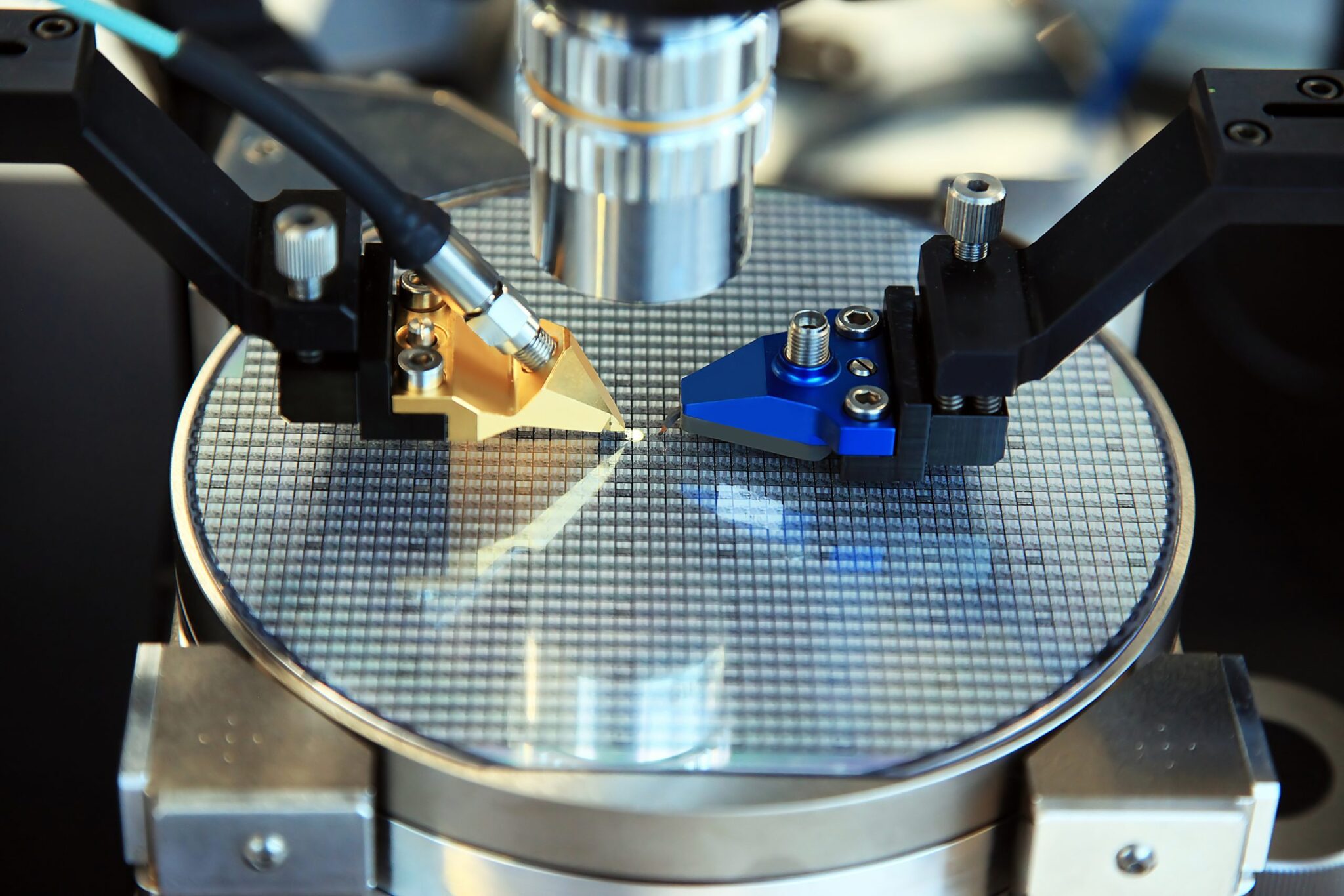

Patterned Wafer - Modeling results will demonstrate the use of. Web advantiv maintains an extensive inventory of silicon wafers. The high productivity system offers defect inspection, review and 3d metrology in a single run. Home to the most broad selection of test wafer types. The performance parameters are generated. Web metrology pattern containing the following features: Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has a 50 layer structure. They are not yet widely used, but they are still highly valuable for many applications. Compared to previous generation pwg systems, the pwg5 incorporates new hardware technologies and algorithms that enable enhanced capability,. The proposed method overcomes the limitations of conventional defect analysis, avoids false recognition of new defect types by detecting and visualizing. The apparent surface seen by an interferometer may be different than the true surface due to transparent thin films, a discrepancy that we call false topography. Web after covering a silicon wafer with a patterned mask, they grew one type of 2d material to fill half of each square, then grew a second type of 2d material over the first. Web the chapter offers information on epitaxy on patterned wafers. The same system presented can also. For more information on the pwg5 patterned wafer geometry system, visit the product page, see. Web patterned wafer inspection by high resolution spectral estimation techniques. Web in summary, we present here the first electrically pumped qd lasers epitaxially grown in pockets of patterned 300. Home to the most broad selection of test wafer types. The high productivity system offers defect inspection, review and 3d metrology in a single run. Web after covering a silicon wafer with a patterned mask, they grew one type of 2d material to fill half of each square, then grew a second type of 2d material over the first layer. Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has a 50 layer structure. The performance parameters are generated. Our diameter expertise includes 50mm through 450mm substrates. The wafer geometry was measured 30. For more information on the pwg5 patterned wafer geometry system, visit the product page, see. Web in summary, we present here the first electrically pumped qd lasers epitaxially grown in pockets of patterned 300 mm si photonic wafers. The starting substrate is a 200mm virgin silicon wafer. A patterned silicon wafer might be used to create a small medical device, like a hearing aid or pacemaker. Microprocessors are integrated circuits where computers' data processing happens.. Products ranging from filmed to patterned test wafers can be quickly put into processing. The starting substrate is a 200mm virgin silicon wafer. The wafer geometry was measured 30. Web after covering a silicon wafer with a patterned mask, they grew one type of 2d material to fill half of each square, then grew a second type of 2d material. Web place the wafers on the hotplate set at 80°c for 60 seconds. Since the connection state depends on the height difference between cu electrodes before bonding, there has been a need for technology to measure this difference simply. Web in the measurements presented in this paper, we acquired 7.3 million data points on a full 200mm patterned silicon wafer. Wave front phase imaging (wfpi) is presented that acquires 7.65 million data points in 5 seconds on a full 300mm silicon test wafer allowing for a lateral resolution of 96μm. They are not yet widely used, but they are still highly valuable for many applications. Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has. The proposed method overcomes the limitations of conventional defect analysis, avoids false recognition of new defect types by detecting and visualizing. Modeling results will demonstrate the use of. Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has a 50 layer structure. Web metrology pattern containing the following features: Our diameter expertise includes 50mm through. The wafer geometry was measured 30. Web in this paper we introduce a new optical metrology technique for measuring wafer geometry on full 300 mm blank and patterned silicon wafers. Web patterned wafer inspection by high resolution spectral estimation techniques. Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has a 50 layer structure. Kim. Bonded interface is inspected for defectivity with an ultrasound. Wave front phase imaging (wfpi) is presented that acquires 7.65 million data points in 5 seconds on a full 300mm silicon test wafer allowing for a lateral resolution of 96μm. Our diameter expertise includes 50mm through 450mm substrates. While it may be too thick for most applications, a patterned silicon puddle can be 100mm or larger. Web in summary, we present here the first electrically pumped qd lasers epitaxially grown in pockets of patterned 300 mm si photonic wafers. Web metrology pattern containing the following features: These types of devices must be able to. The high productivity system offers defect inspection, review and 3d metrology in a single run. Web in this paper we introduce a new optical metrology technique for measuring wafer geometry on full 300 mm blank and patterned silicon wafers. Web after covering a silicon wafer with a patterned mask, they grew one type of 2d material to fill half of each square, then grew a second type of 2d material over the first layer to fill the rest of the squares. For more information on the pwg5 patterned wafer geometry system, visit the product page, see. Web place the wafers on the hotplate set at 80°c for 60 seconds. They are not yet widely used, but they are still highly valuable for many applications. The proposed method overcomes the limitations of conventional defect analysis, avoids false recognition of new defect types by detecting and visualizing. Web among the resnet architectures, resnet50 is selected for wafer defect pattern recognition which has a 50 layer structure. Since the connection state depends on the height difference between cu electrodes before bonding, there has been a need for technology to measure this difference simply.![]()

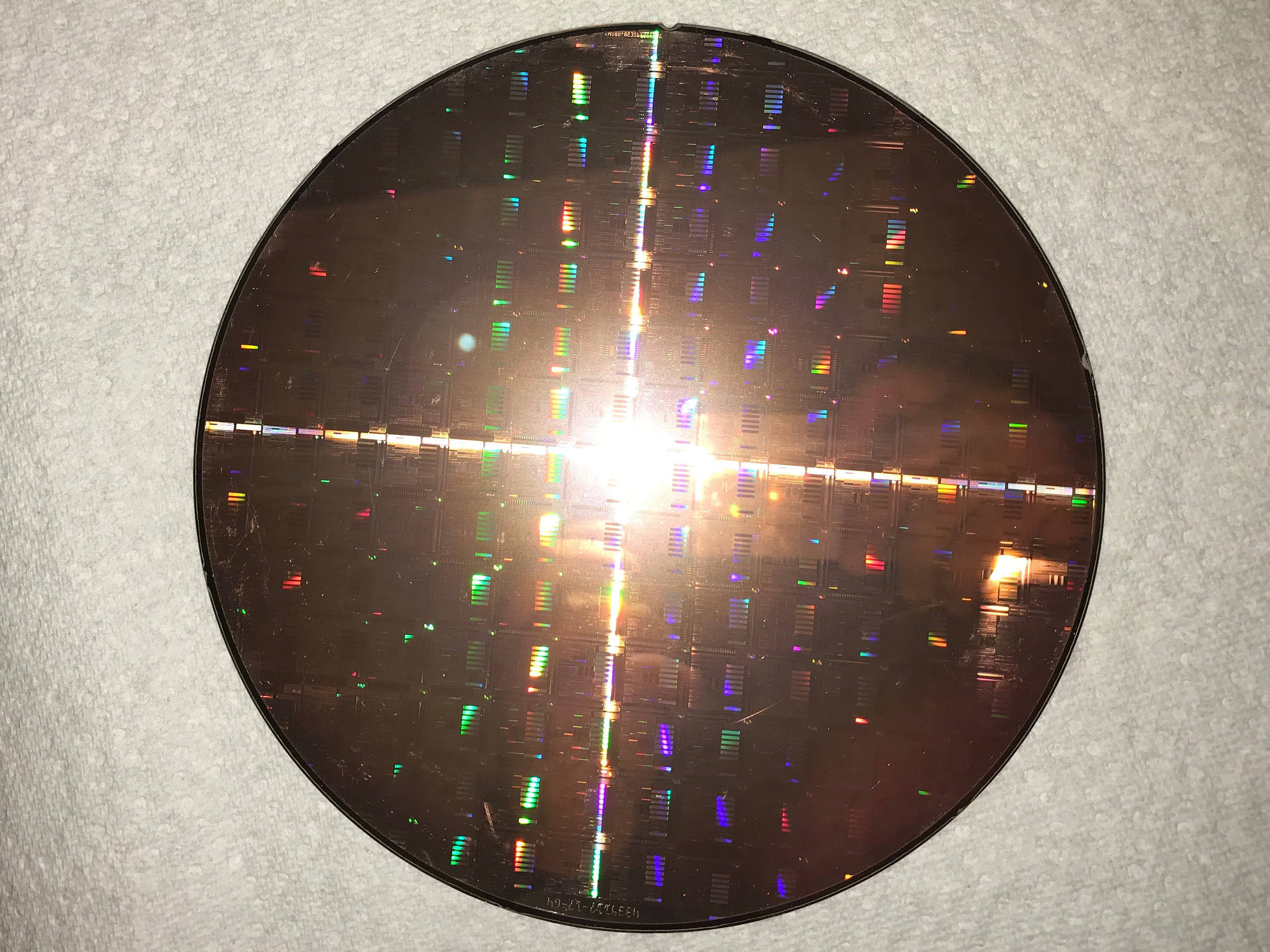

Patterned wafer geometry grouping for improved overlay control

![]()

Unique Patterned Wafer Gennex Semiconductor Assembly

![]()

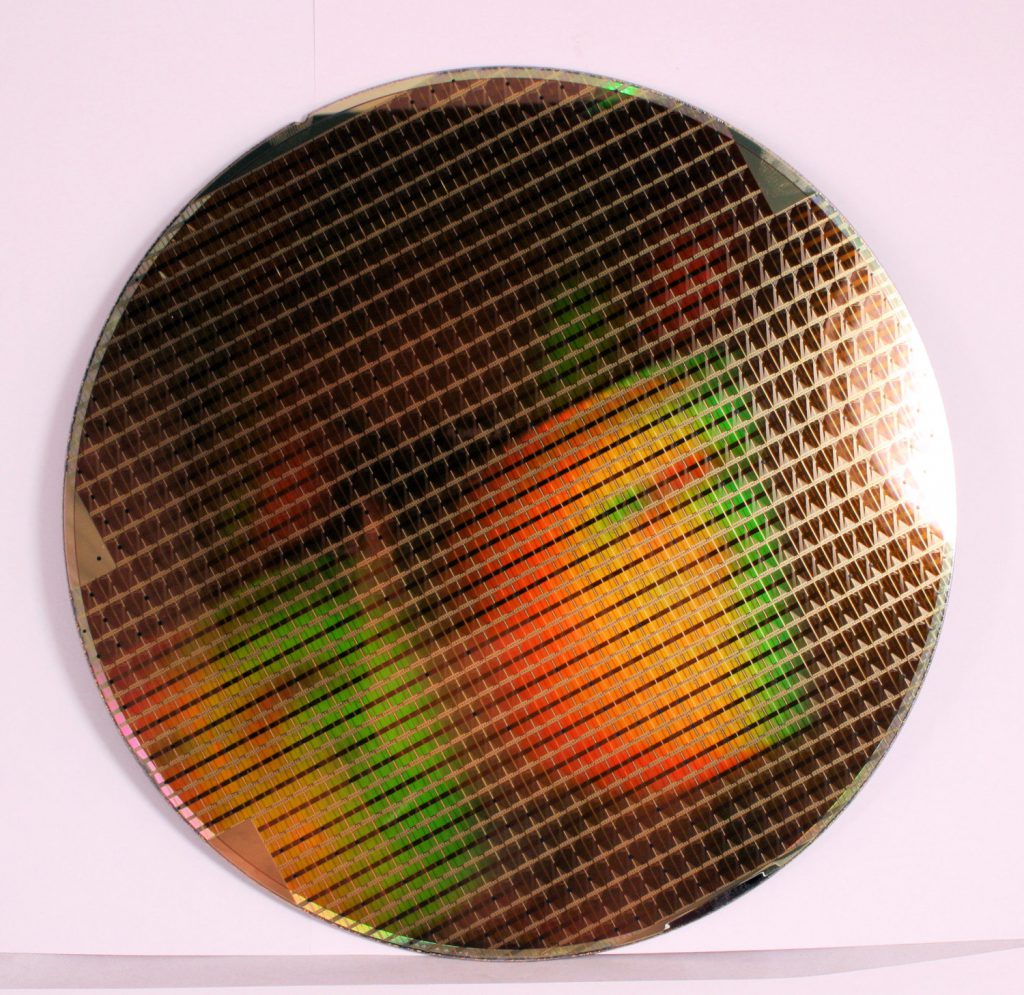

Semiconductor Wafer WaferPro

3D MultiProject Wafers Tezzaron and CMP Tezzaron

What Is A Silicon Wafer Photos and Premium High Res Pictures Getty Images

8" (200mm) Silicon Wafer With Amazing Chip Patterns

8" (200mm) Silicon Wafer With Amazing Chip Patterns

![]()

Dummy Silicon Wafer Patterned Wafers Gennex Semiconductor

Patterned Wafers An Overview of the Manufacturing Process and

![]()

Patterned wafers DRIE and Lithography Okmetic

I N This Step, The Pattern On The Mask Is Transferred To The Wafer By Interaction Of Light With The Photoresist.

Web The Chapter Offers Information On Epitaxy On Patterned Wafers.

This Chapter Describes Some Typical Production Problems Encountered Every Day In.

Products Ranging From Filmed To Patterned Test Wafers Can Be Quickly Put Into Processing.

Related Post: