Double Patterning

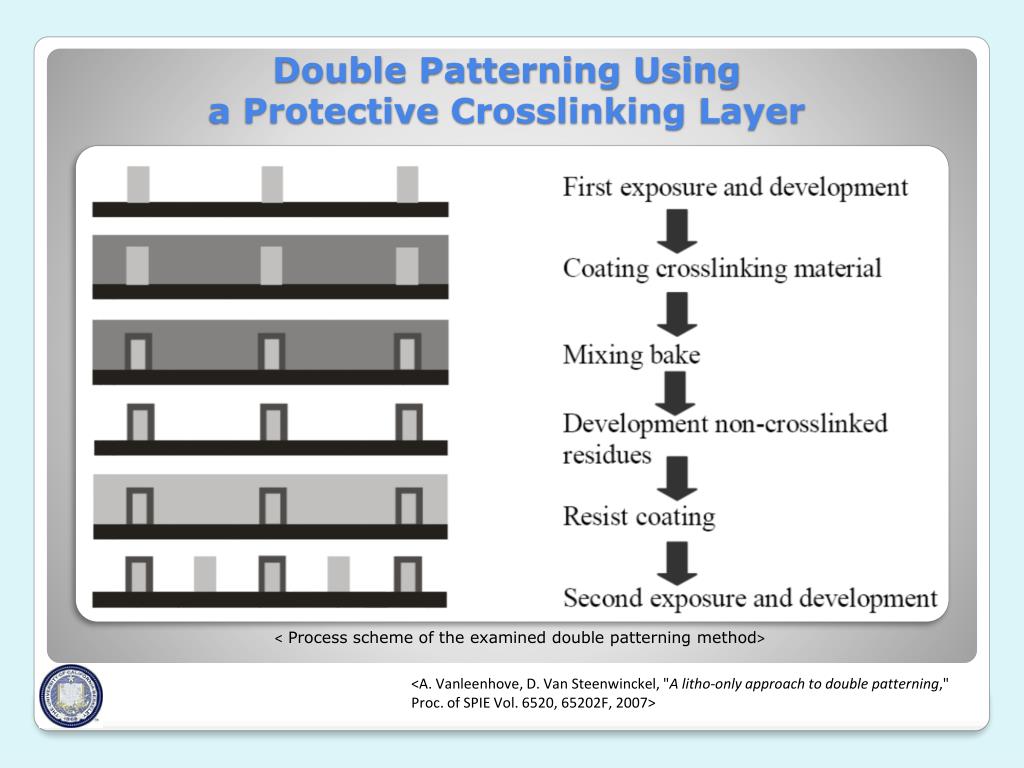

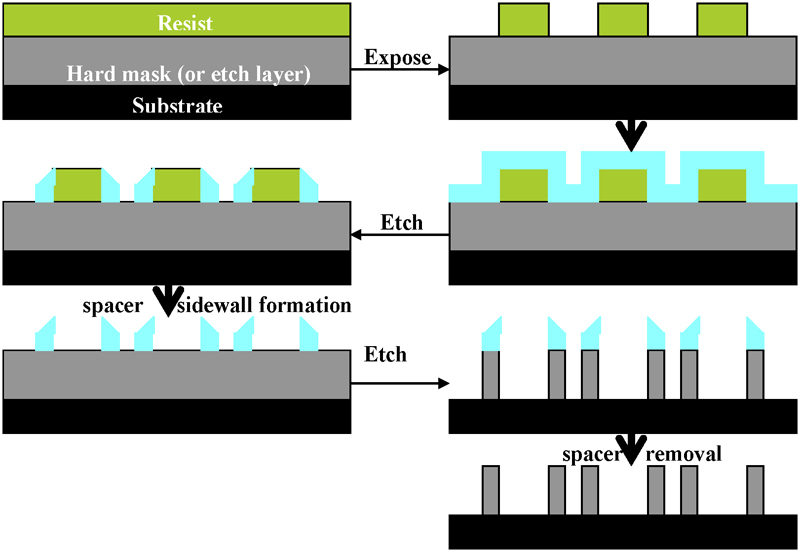

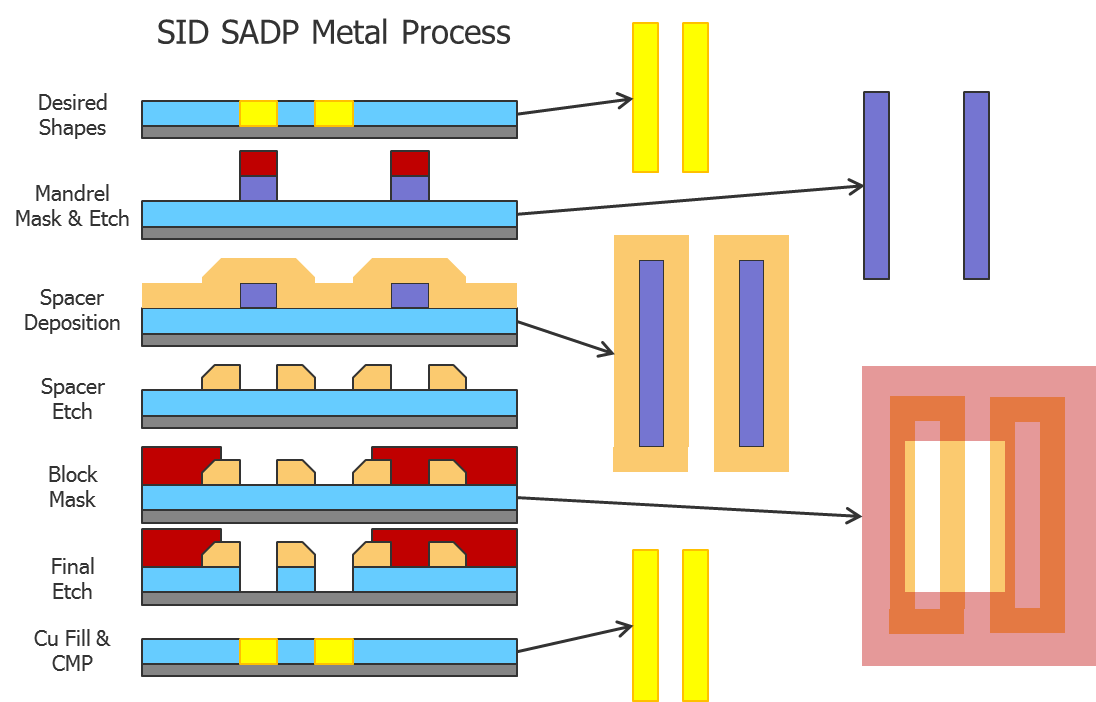

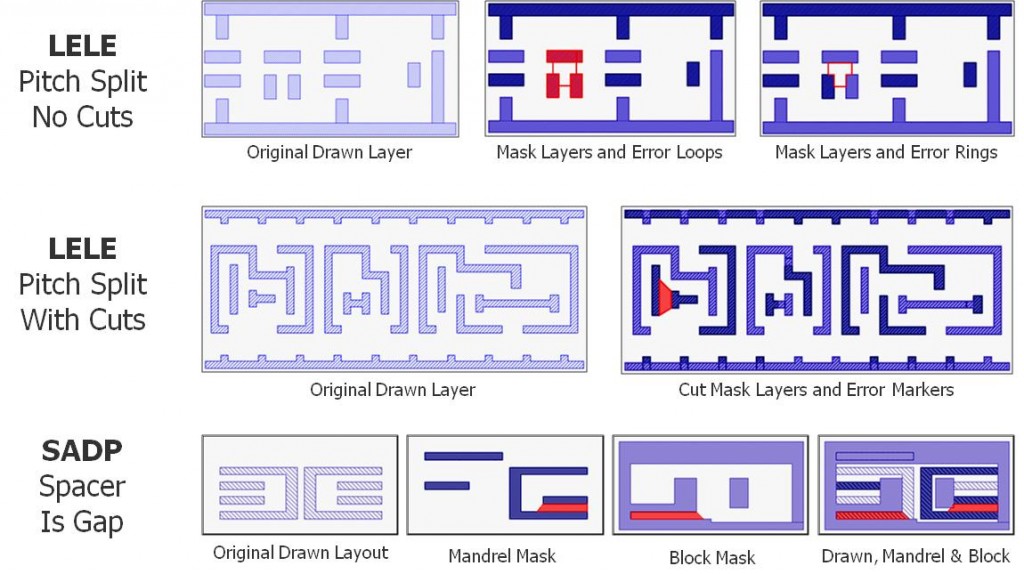

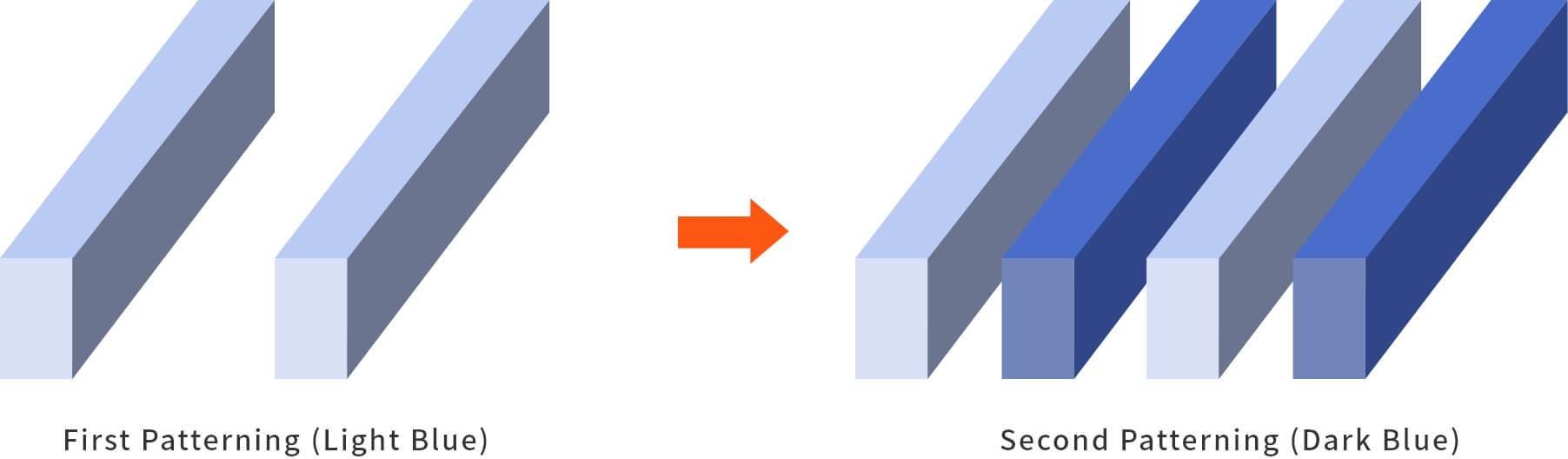

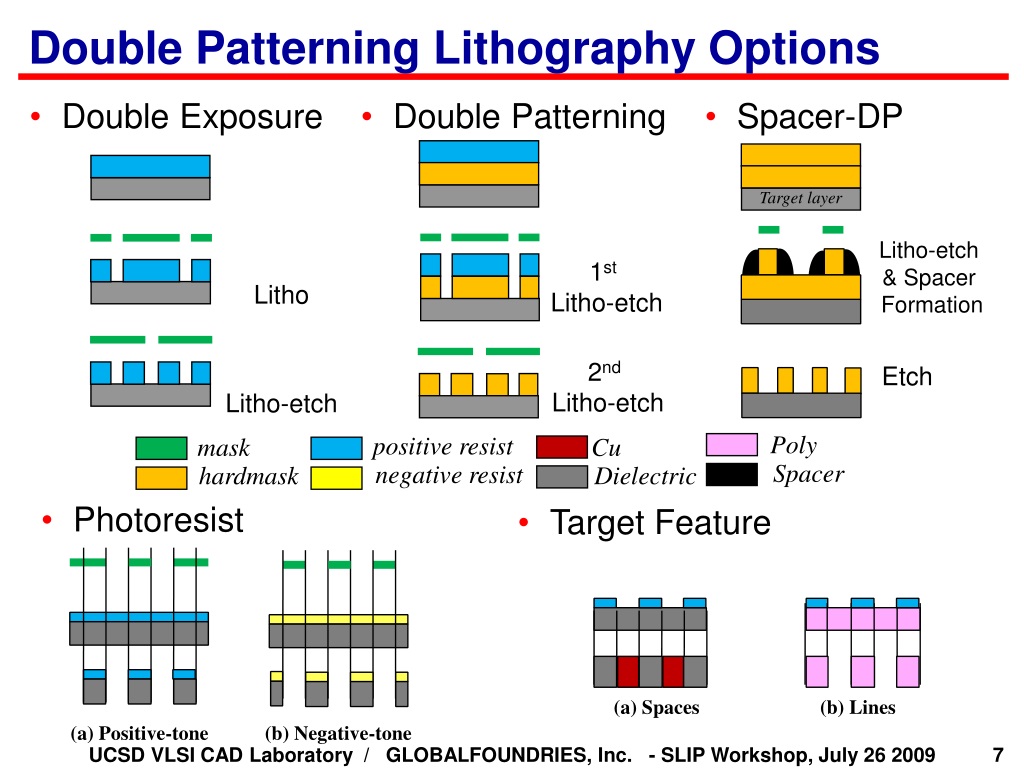

Double Patterning - 43k views 15 years ago. Web this video talks about patterning of transistors in a sram cell and why self aligned double patterning is preferred for patterning the fins for an finfet transistor. Web double patterning has become the semiconductor industry’s preferred technique in this case. Double patterning is more sensitive to variations in process. Introduction to double patterning which is used extensively for printing transistors and other features in. Because euv hasn't come through. Errors in dose, focus, or mask overlay will affect potential yield. Web abstract—double patterning technology (dpt) is a most likely lithography solution for 32/22nm technology nodes as of 2008 due to the delay of extreme ultra violet lithography. Web double patterning is a widely used technique in advanced semiconductor manufacturing processes, especially at smaller process nodes. It is expected to be necessary for the 10 nm and 7 nm node. Because euv hasn't come through. Web abstract—double patterning technology (dpt) is a most likely lithography solution for 32/22nm technology nodes as of 2008 due to the delay of extreme ultra violet lithography. Enabling dimensions beyond lithography resolution limits. Web double patterning can be implemented in three ways: It is expected to be necessary for the 10 nm and 7 nm. Web double patterning can be implemented in three ways: Double patterning is more sensitive to variations in process. It is expected to be necessary for the 10 nm and 7 nm node. It is suitable for beginners who have learned this basic stitch. There are three main double pattern techniques are there. See, already we have two correct answers for the same acronym! Web this chevron crochet blanket is easy as it only uses double crochet stitches and chains. There are five methods of entropy (slope entropy, permutation entropy, symbolic dynamic entropy, and. Web this video talks about patterning of transistors in a sram cell and why self aligned double patterning is. David won the award for the best tutorial at the 2012 tsmc oip for his presentation, along with peter hsu of tsmc, on finding and fixing double patterning errors in 20nm. Web like the earlier manufacturing tools, the double pattern checking and decomposition capability requires a whole new software engine under the hood to properly analyze the layout. There are. There are three main double pattern techniques are there. It is expected to be necessary for the 10 nm and 7 nm node. Web this paper explores the application of slope entropy in fault diagnosis. Web double patterning mitigates the impact of diffraction in optical lithography. Web double patterning has become the semiconductor industry’s preferred technique in this case. Enabling dimensions beyond lithography resolution limits. Introduction to double patterning which is used extensively for printing transistors and other features in. Web double patterning is a widely used technique in advanced semiconductor manufacturing processes, especially at smaller process nodes. Web this chevron crochet blanket is easy as it only uses double crochet stitches and chains. Web double patterning can be. Web this paper explores the application of slope entropy in fault diagnosis. It is suitable for beginners who have learned this basic stitch. Chipmakers always try to make electronic. Web double patterning can be implemented in three ways: David won the award for the best tutorial at the 2012 tsmc oip for his presentation, along with peter hsu of tsmc,. Opc can design for ideal process conditions. For process engineers around the world, however, dp is double the fun because of the new opportunities the technology offers. Enabling dimensions beyond lithography resolution limits. Web this chevron crochet blanket is easy as it only uses double crochet stitches and chains. Web this video talks about patterning of transistors in a sram. Enabling dimensions beyond lithography resolution limits. Let’s see it in detail. Introduction to double patterning which is used extensively for printing transistors and other features in. Web the way that a designer will interact with the constraints that double patterning (dp) brings is very dependent on the design methodology used. Opc can design for ideal process conditions. It is expected to be necessary for the 10 nm and 7 nm node. See, already we have two correct answers for the same acronym! Web abstract—double patterning technology (dpt) is a most likely lithography solution for 32/22nm technology nodes as of 2008 due to the delay of extreme ultra violet lithography. Web do you want designers to be able. Web do you want designers to be able to seed double patterning, which can be important in analog to guarantee better control over some of the parasitics. Enabling dimensions beyond lithography resolution limits. Web the way that a designer will interact with the constraints that double patterning (dp) brings is very dependent on the design methodology used. Web double patterning is a technique used in the lithographic process that defines the features of integrated circuits at advanced process nodes. Introduction to double patterning which is used extensively for printing transistors and other features in. Let’s see it in detail. Web tsmc is planning to adopt double patterning extensively at 20nm, despite the high cost of doing so. Web this chevron crochet blanket is easy as it only uses double crochet stitches and chains. Errors in dose, focus, or mask overlay will affect potential yield. It is suitable for beginners who have learned this basic stitch. Because euv hasn't come through. Web this paper explores the application of slope entropy in fault diagnosis. It is expected to be necessary for the 10 nm and 7 nm node. Web like the earlier manufacturing tools, the double pattern checking and decomposition capability requires a whole new software engine under the hood to properly analyze the layout. There are three main double pattern techniques are there. Opc can design for ideal process conditions.

PPT Double Exposure/Patterning Lithography PowerPoint Presentation

Double patterning lithography double the trouble or double the fun?

SelfAligned Double Patterning—Part Deux

Resources ECE 595AL Lecture 4 Immersion Lithography and

Double Patterning to the rescue (LELE, LFLE, SADP) Part 1 YouTube

PPT Double Patterning Technology Friendly Detailed Routing PowerPoint

Multiple Patterning Semiconductor Engineering

What is Double Patterning?

PPT Is Overlay Error More Important Than Interconnect Variations in

Double Patterning to the rescue (Self Aligned Double Patterning) Part

For Process Engineers Around The World, However, Dp Is Double The Fun Because Of The New Opportunities The Technology Offers.

Web Double Patterning Can Be Implemented In Three Ways:

Web Double Patterning Has Become The Semiconductor Industry’s Preferred Technique In This Case.

But Unlike The Earlier Layout Issues, Double Patterning Violations Can Be Much More Pervasive, And Fixing Them Is Mandatory, Not Just Recommended.

Related Post: